# Megalithic Microwave Signal Processing for Phased-Array Beamforming and Steering

Takashi Ohira, *Member, IEEE*, Yoshinori Suzuki, Hiroyo Ogawa, *Member, IEEE*,

and Hideki Kamitsuna, *Member, IEEE*

**Abstract**—A microwave signal processing (MSP) architecture is presented for active phased array beam forming and steering. A large scale network, comprising 63 power dividers and 32 pairs of vector-synthetic phase/amplitude controllers, has been successfully developed in an 11 mm × 13 mm GaAs monolithic microwave integrated circuit (MMIC). It has a huge integration level of 128 metal–semiconductor field effect transistors (MESFET's), 448 spiral inductors, 527 metal–insulator–metal (MIM) capacitors, and 357 ion-implanted resistors. The expected 360° phase is successfully obtained at all the output ports. Vector error standard deviations exhibited are within 0.38-dB root-mean square (rms) and 2.8° rms over the bandwidth of 20 MHz at 2.5 GHz. This megalithic chip could mark an epoch in phased array systems.

**Index Terms**—Active phased arrays, beamforming, cold FET's, microwave attenuators, microwave phase shifters, microwave signal processing, MMIC's, power dividers/combiners, satellite communication onboard systems, varistors, wafer-scale integration.

## I. INTRODUCTION

TRANSMITTED power requirements in satellite communication systems have been steadily increasing in recent years, and the numbers of satellite beams is also predicted to increase annually because of frequency reuse and the growing traffic demand. As a means of meeting these requirements, global and regional access satellite communication systems featuring multiple-beam LEO or GEO satellites have recently been proposed. In developing satellite of this type, the use of an active phased array with spatial power combining is considered a viable means of enabling the radiation of high-power multiple beams. In this approach, the beamforming network (BFN) is expected to provide the following functions:

- 1) precise pointing of each beam to the target area despite possible deviations of the array system components and satellite attitude;

- 2) forming of nulls exactly onto the neighboring area where frequency reuse could create problems;

- 3) providing of reconfiguration in case a failure occurs in any radiated beam.

Precise beam and null pointing is especially important in high-gain reflector antenna systems [1]. Digital beamforming

(DBF) or digital signal processing (DSP) has been employed in some practical systems [2], [3] to achieve adaptive beam steering. In multi-carrier systems such as satellite transponders, however, DSP dissipates a large amount of dc power as the number of the carriers increases. It also requires dozens of high-speed and high-resolution digital-to-analog converters (DAC's).

Another approach to beam steering is to introduce control circuits [4]–[9] in an analog BFN. This paper presents a direct microwave signal processing (MSP) architecture which employs this approach to achieve active phased array beamforming and steering. The architecture's highly dense constituent circuit topologies and the superior megalithic integration achieved with it are described.

## II. BFN ARCHITECTURE

The BFN is the key device for achieving an active phased array. Butler's hybrid matrix network [10] is commonly used as BFN architecture, because it can create multiple beams simultaneously with a limited scale microwave circuit. Unfortunately, the hybrid matrix is useful only for fixed beamforming and is unable to steer each beam (see Table I). To steer each beam independently, the BFN must distribute the RF input signal to all the radiators with a specific phase. Each distributed and weighted signal has to be combined with the signals of other beams. Amplitude is also controlled for beam pattern shaping and side lobe suppression. Therefore, the BFN must be equipped with a proportional number of power divider/combiners, variable phase shifters, and attenuators to the number of beams times the radiator elements. The MSP should have the following functions:

input—division—complex weighting—combining—output.

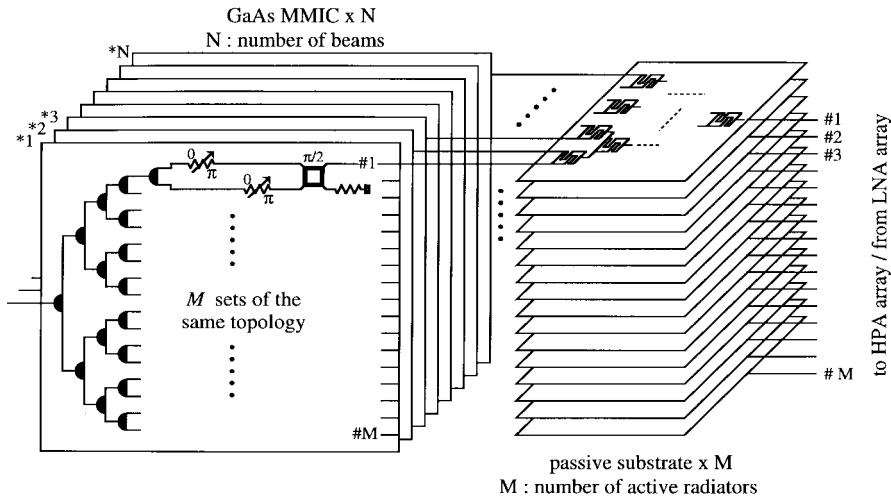

An interconnected three-dimensional (3-D) structure [11] loaded with  $N$  GaAs monolithic microwave integrated circuit (MMIC) chips followed by  $M$  sets of  $N$ -way passive combiner substrate is proposed to form a compact hardware (see Fig. 1).  $M$  and  $N$  are the number of radiators and beams, respectively. Since the beamforming function for each beam is integrated in a single chip, we label this BFN configuration “single-chip-per-beam.” Monolithic integration of this huge scale circuit is achieved through a new MSP architecture as shown in Fig. 1, featuring a 64-way pyramidal power distribution and phase/amplitude control without employing any conventional phase shifters. Full 360° phase is generated on a

Manuscript received March 31, 1997; revised July 31, 1997.

T. Ohira, Y. Suzuki, and H. Ogawa are with the NTT Wireless Systems Laboratories, Yokosuka 239, Japan.

H. Kamitsuna is with the NTT Electronics Corporation, Yokosuka 239, Japan.

Publisher Item Identifier S 0018-9480(97)08336-1.

Fig. 1. Proposed  $M \times N$  multiple-beamforming and steering network architecture. Main features: 1) very high-level integration, i.e., all the control circuits for each beam are in a single GaAs MMIC chip and 2) unique circuit topologies for pyramidal cascadable power divider and  $M$ -parallel vector-synthetic amplitude/phase controllers.

TABLE I

|                                      |    | separate                             | multi-port transmitter                          | active phased array transmitter |                                          |                                                             |

|--------------------------------------|----|--------------------------------------|-------------------------------------------------|---------------------------------|------------------------------------------|-------------------------------------------------------------|

| Configuration                        |    |                                      |                                                 |                                 |                                          |                                                             |

| Signal processing                    |    | N/A                                  | microwave high-level stage                      |                                 | microwave low-level stage                |                                                             |

| Power combining                      |    | N/A                                  | in-circuit combining                            |                                 | spatial power combining                  |                                                             |

| Power flexibility                    |    | limited by each PA                   | automatically assigned according to the traffic |                                 |                                          |                                                             |

| Beam steering                        |    | discrete switching among fixed beams |                                                 |                                 | continuous and independent beam steering |                                                             |

| Phase adjust                         |    | N/A                                  | hardware cut-and-try trimming                   |                                 | electronically programmable              |                                                             |

| Power dissipation or heat generation | DC | N/A                                  | none                                            |                                 | very low                                 | fairly high due to high-resolution high-speed multiple DACs |

|                                      | RF | N/A                                  | high due to multi-stage hybrid matrix           | very low                        |                                          | N/A                                                         |

SW: switch matrix, BM: butler matrix, DAC: digital-to-analog converter, MSP: microwave signal processing, DSP: digital signal processing.

vector-synthetic or vector-modulator principle by orthogonally coupled twin attenuators. The proposed circuit topologies to achieve this architecture are the pyramidal cascadable power divider (PcPD) and the phase-invertible variable attenuator (PiVA).

### III. PYRAMIDALLY-CASCADABLE POWER DIVIDER (PcPD)

The Wilkinson power divider/combiner is well known and widely used as the key basic three-port constituent passive device for MIC's and MMIC's. The device's unique feature is that it provides two-way signal distribution with completely symmetrical amplitude and phase. It also features excellent isolation between its two output ports as well as simultaneous impedance matching at all three of its ports. In spite of its advantages, the Wilkinson divider is composed of quarter

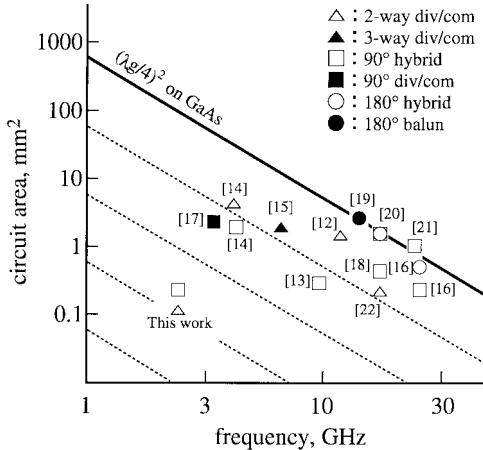

wavelength long distributed-constant transmission lines resulting in large physical space; thus its topology is not practical for monolithic integration, especially at lower frequencies. Various attempts such as folded microstrip [12], quasi-lumped circuit [14], and a 3-D MMIC approach [22], have been reported to reduce the size of passive basic circuits. Even though these techniques brought considerable size reduction in comparison with the conventional quarter wavelength circuit (Fig. 2), much more reduction is required for MSP. As a means of achieving this, we present a novel and simple circuit configuration for the cascaded signal division. The key technical point is how to simplify the circuit configuration without sacrificing electric performance, e.g., impedance matching, insertion loss, and isolation between output ports. The complex iterative impedance method is introduced as a useful technique to meet these opposing requirements.

Fig. 2. Passive circuit size reduction for high-integration MMIC's.

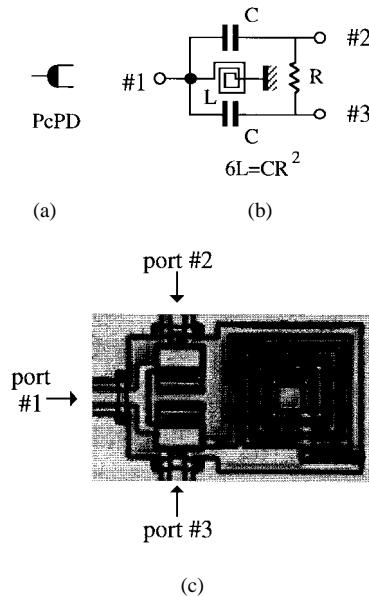

Fig. 3. Pyramidal cascadable Power Divider (PcPD). (a) Symbol. (b) Schematic diagram. (c) Prototype fabricated on GaAs substrate. Size: 0.12 mm².

In lumped-element MMIC layouts, spiral inductors often occupy much more area than capacitors or resistors. This is physically inevitable because the substrate material, e.g., GaAs, is not a magnetic medium, while capacitors employ a highly permittive medium in their interelectrode insulators. An effective design solution for high density MSP is to reduce the total number of inductors and the absolute inductance value of each inductor. The circuit topology proposed here, shown in Fig. 3, employs only one inductor, whose inductance is one third of that used in the previously reported configuration [14]. It is a drastically simplified design topology, yet it keeps the basic characteristics of simultaneous three-port impedance matching, symmetrical two-way power division, and isolation between two output ports, if  $6L = CR^2$ . (See the Appendix for details.)

We developed a prototype circuit designed to function at  $2.5 \text{ GHz} \pm 10 \text{ MHz}$ , i.e., S-band communication satellite frequency. The element constants determined are  $R = 100 \Omega$ ,

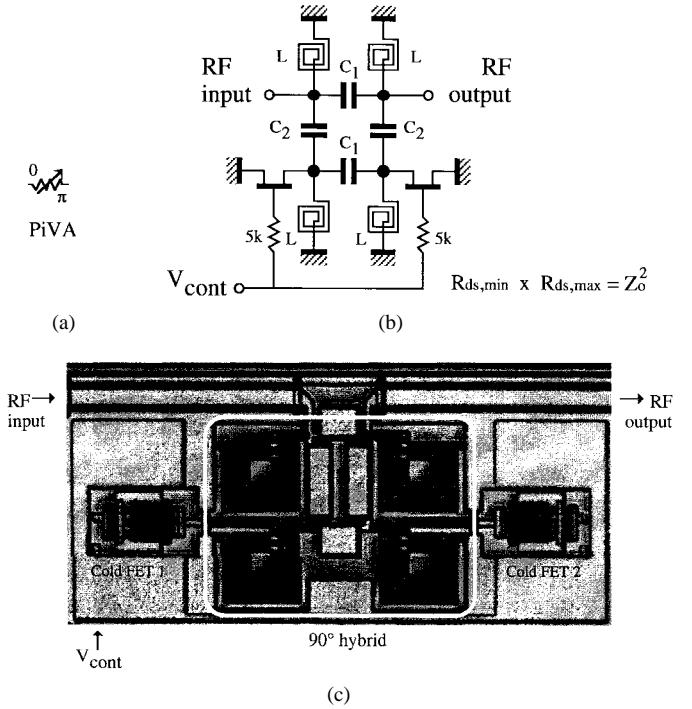

Fig. 4. Phase-invertible Variable Attenuator (PiVA). (a) Symbol, (b) schematic diagram, and (c) prototype fabricated on GaAs substrate. It measures  $0.64 \text{ mm}^2$ , including the  $\pi/2$  hybrid ( $0.24 \text{ mm}^2$ ; inside the white line), twin FET's and I/O feed lines. The FET's are called "cold FETs" since they have zero dc drain-source voltage and zero dc gate current.

$L = 1.5 \text{ nH}$ , and  $C = 0.9 \text{ pF}$ . Fig. 3(c) shows a prototype of the circuit fabricated on a GaAs substrate; occupies only  $0.12 \text{ mm}^2$  of MMIC space. This circuit is believed to be the smallest power divider ever reported at this frequency (Fig. 2). This design enables us to achieve a  $2^n$ -way pyramidal power distribution in a very compact area.

#### IV. PHASE-INVERTIBLE VARIABLE ATTENUATOR (PiVA)

The next approach is to combine a number of functions in a single circuit. The proposed circuit topology, PiVA, performs continuously variable attenuation and  $\pi$  phase inversion. The concept of PiVA, shown in Fig. 4, utilizes a pair of cold FET's interlocked by a single control voltage. To carry out the phase inverter function, the gate width is designed to satisfy the relationship:

$$R_{ds, \min} < Z_o < R_{ds, \max}$$

where  $R_{ds}$  is the drain-source variable resistance of the cold FET and  $Z_o$  is the characteristic impedance of the  $90^\circ$  hybrid achieved using the  $L$  and  $C$  components. With the help of circuit symmetry [23], the lumped constants are deduced in the same manner as the PcPD, cf. the Appendix, resulting in

$$C_1 = \frac{1}{\omega Z_o}, \quad C_2 = \frac{\sqrt{2}}{\omega Z_o}, \quad L = \frac{1}{1 + \sqrt{2}} \frac{Z_o}{\omega}.$$

The forward transfer phase  $\angle S_{21}$  exhibits  $\pm 90^\circ$  phase shift when  $R_{ds} < Z_o$  or  $R_{ds} > Z_o$ , respectively. The key design point is to obtain symmetrical attenuation characteristics

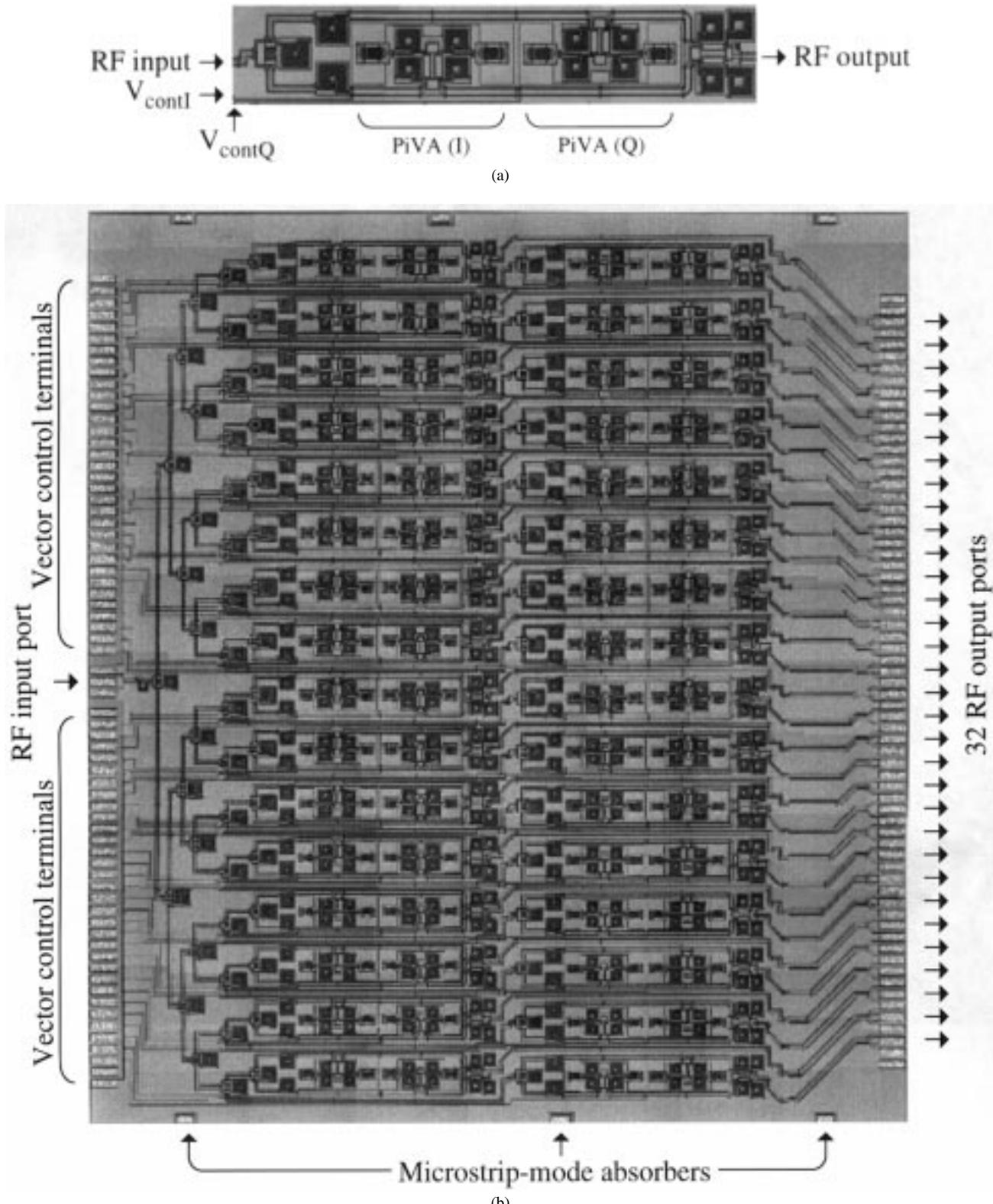

Fig. 5. View of the developed prototype GaAs megalithic BFN. (a) A vector synthesizer portion for attaining an orthogonal and complete constellation, i.e., full 360° phase and arbitrary amplitude control and (b) an entire microwave signal processing function for 32-element phased-array beamforming/steering integrated in an 11 mm  $\times$  13 mm MMIC chip.

between the two phase states such that

$$R_{ds, \min} \times R_{ds, \max} = Z_o^2.$$

A PiVA prototype matching that of PcpD was developed and also designed to function at 2.5 GHz  $\pm$  10 MHz. To minimize

the inductance, characteristic impedance is maintained at the low level of as  $Z_o = 33.3 \Omega$ , resulting in  $L = 0.85 \text{ nH}$ ,  $C_1 = 1.9 \text{ pF}$ , and  $C_2 = 2.7 \text{ pF}$ . In the fabricated prototype, shown in Fig. 4(c), the PiVA occupies only  $0.64 \text{ mm}^2$  of the GaAs substrate. This cell requires only one control signal, hence it is

very space efficient. Based upon the vector-synthetic principle, arbitrary phase and amplitude is generated by orthogonally combining a pair of PiVA cells. The complex transfer function  $S_{21}$  of the combined circuit is formulated as

$$S_{21} = \frac{1}{2} \left( \frac{R_{ds,1} - Z_o}{R_{ds,1} + Z_o} + j \frac{R_{ds,2} - Z_o}{R_{ds,2} + Z_o} \right)$$

where  $R_{ds,1}$  and  $R_{ds,2}$  are the drain-source resistances of the cold FET's used in each PiVA cell. These resistances are controlled by a pair of external dc voltage supplies. This vector-synthetic phase generator is more linear than other phase shifters [7] based on varactor diodes, since the nonlinear Schottky-junction capacitances introduce intermodulation distortion.

## V. PROTOTYPE GAAS MMIC

Utilizing the high-integration circuit topologies proposed in the two previous sections, a prototype "single chip per beam" BFN is fabricated on an 11 mm  $\times$  13 mm GaAs substrate as shown in Fig. 5. It consists of:

- 1) one RF input port;

- 2) a six-stage pyramidal divider;

- 3) 32 sets of vector synthesizers;

- 4) 32 RF output ports;

- 5) 32 pairs of control dc terminals;

- 6) peripheral ground terminals.

The 32-way divider provides uniform-phase and uniform-amplitude signals. Amplitude and phase of each signal are controlled in the vector synthesizer stage. The integrated elements total more than one thousand, i.e., 128 metal-semiconductor field effect transmitter (MESFET's), 448 spiral inductors, 527 metal-insulator-metal (MIM) capacitors, and 357 ion-implanted resistors. To accomplish this high integration level, a coplanar structure is employed which eliminates via holes. To suppress unwanted microstrip-mode resonance,  $Q$ -damping elements are placed on the edge of the chip.

## VI. TEST PROCEDURE AND RESULTS

The megalithic BFN performance was measured at the S-band satellite communication frequencies using a wafer probe station. The DUT has 1 input port and 32 output ports. A custom-built multiple-port probe card was employed to measure the  $[S]$  parameters at the port under test as well as to terminate the other 31 ports. Thus, a two-port network analyzer is used sequentially port by port. Two dc voltage supplies are necessary to control the output vector, in-phase and quadrature, for each port.

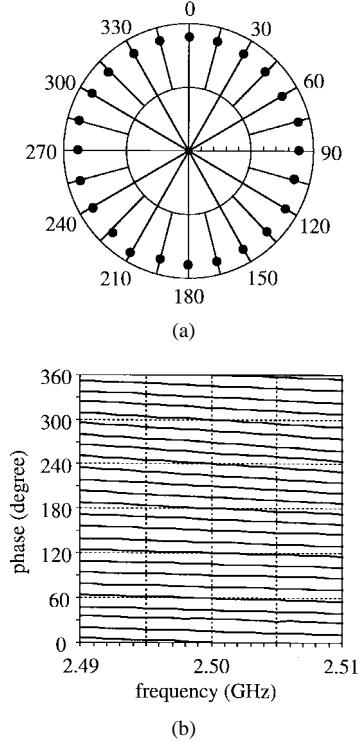

First, port 1 was tested while the others are terminated to  $50\Omega$  loads. The control voltages were imposed only for port 1. The voltages were adjusted so as to obtain endless phase shift in a constant amplitude. The expected  $360^\circ$  phase was successfully attained, as depicted in the polar plot of Fig. 6(a) in  $15^\circ$  steps. In each of the 24 states, phase variation was measured and is depicted in Fig. 6(b) as a function of frequency. The phase differences between two adjacent states are held almost constant in this frequency range.

Fig. 6. The measured phase control performance of the megalithic BFN. (a) Representations of a full  $360^\circ$  vector synthesis in  $15^\circ$  steps measured at the center frequency and (b) measured phase variation as a function of frequency over the 24 phase states.

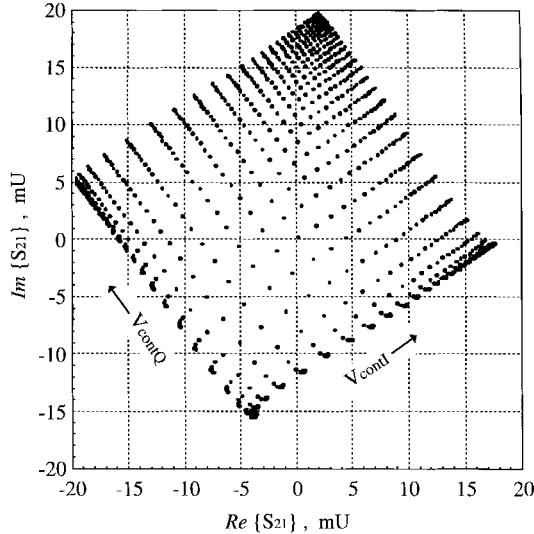

Next, the orthogonal control voltages were swept over their full span to observe the entire constellation. The synthesized vector for this two-dimensional (2-D) trace is plotted as shown in Fig. 7. It demonstrates an orthogonal and complete constellation. This vector synthesis test was completed at ports 1–32. No defects were found at any port.

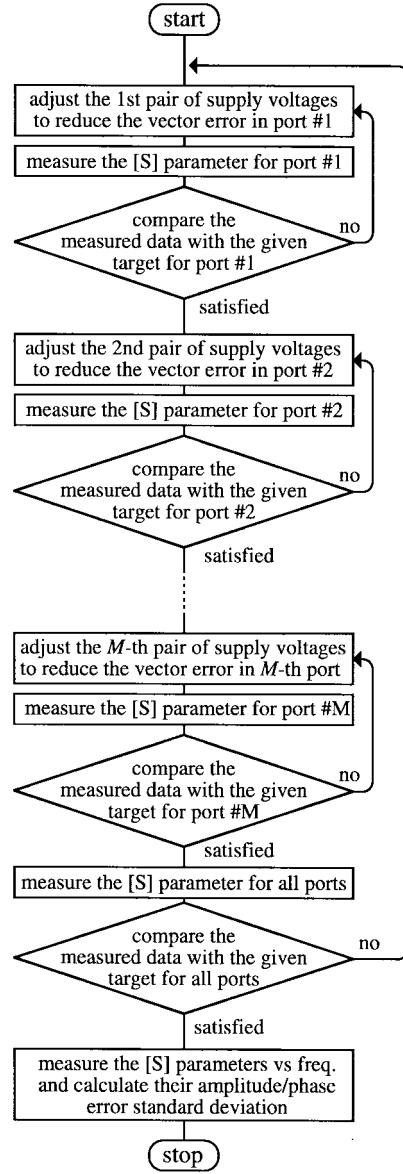

Then, full-32-port amplitude/phase adjusting was attempted. For automatic measurement and adjusting, a setup composed of a vector network analyzer, 32 pairs of GP-IB controlled dc voltage supplies, and a control computer were added to the wafer probe station. The 32 pairs of amplitude/phase targets are obtained from the system requirements. The supply voltages are sequentially controlled by the computer to minimize the differences:

$$\Delta a_i = a_i - \alpha_i \text{ and } \Delta \varphi_i = \varphi_i - \Phi_i; \quad i = 1, 2, 3, \dots, M$$

where  $a_i$  and  $\varphi_i$  are measured values,  $\alpha_i$  and  $\Phi_i$  are the given target for the  $i$ th port, and  $M$  is the number of ports ( $M = 32$ ). Some errors are caused by the mutual electromagnetic coupling between adjacent output ports since they lie densely side by side as shown in Fig. 5. These errors are serious when accuracy is required in the phased array system. The computer algorithm to overcome this problem is shown in Fig. 8. In this flow chart, the inner feedback loops reduce the errors in each port. The outer feedback loop reduces the errors due to the mutual coupling. A 2-D modified Newton method is employed in fine voltage adjusting for each port. Using this iterative method enabled the correlated errors to be removed. All that remains are the residual random error, which was a very low 0.1-dB rms and  $0.7^\circ$  rms at the center frequency.

Fig. 7. Constellation of the synthesized vector observed at port 1: The parameter  $S_{21}$  is measured and plotted in the real-imaginary chart. The unit  $mU$  is used for  $\times 10^{-3}$ . The in-phase and quadrature control dc voltages ( $V_{\text{cont } I}$  and  $V_{\text{cont } Q}$ ) are swept over the span of 0 to  $-1.5$  V with the step of 50 mV. The constellation is skewed from the axes because of a fixed phase delay between the input and output ports. The nonuniform density of points comes from the dc control characteristics of the attenuators. This square shape is good in its orthogonality and completeness.

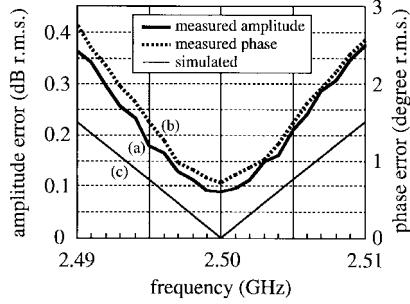

Finally, all the supply voltages were set at the above converged voltage levels, and the vector variation versus frequency was measured for all the ports. At each frequency, the 32 vector errors, i.e.,  $\Delta a_i$  and  $\Delta \varphi_i$ ;  $i = 1$  to 32, were statistically evaluated by using the standard deviations defined as

$$\sigma_{\Delta a} = \frac{1}{M} \sqrt{M \sum_{i=1}^M \Delta a_i^2 - \left( \sum_{i=1}^M \Delta a_i \right)^2}$$

$$\sigma_{\Delta \varphi} = \frac{1}{M} \sqrt{M \sum_{i=1}^M \Delta \varphi_i^2 - \left( \sum_{i=1}^M \Delta \varphi_i \right)^2}.$$

The resultant vector deviations are within 0.38 dB rms and  $2.8^\circ$  rms over the bandwidth of 20 MHz at 2.5 GHz as shown in Fig. 9. The dc current observed at each control terminal is less than  $50 \mu\text{A}$  throughout this test because of the very high dc gate impedance of cold FET's.

This performance is suitable for onboard active phased array applications. The designed BFN is fully reciprocal so that it can be applied not only to transmitters but also to receivers. Since this design is both space efficient and nonheat-generating, it could be applied to multibeam BFN's by piling up the BFN chips with high-isolation packages [11] for each beam control layer as shown in Fig. 1.

## VII. CONCLUSION

Several novel lumped-constant circuit topologies have been presented for high density integration. An innovative huge scale circuit, being fully functional as a beamforming and steering network, has been designed and fabricated in a

Fig. 8. Double-loop feedback algorithm for full- $M$ -port amplitude/phase adjusting: The inner feedback loops reduce the errors in each port. The outer feedback loop reduces the errors due to mutual coupling between adjacent ports.

single GaAs MMIC chip. In spite of this huge scale of integration, no defects were found on the chip. Full  $360^\circ$  phase was observed at the target frequency. The expected vector synthesis was successfully completed at all the output ports. Amplitude and phase are controlled by the computer program to converge onto the target accurately with a double-closed-loop iterative algorithm. Residual error was a low 0.38 dB rms and  $2.8^\circ$  rms in the 20 MHz at S-band range. The chip is ready to go onboard for practical communication satellites. This megalithic development can be a major step toward achieving "pseudo-" LSI signal processing directly at microwave frequencies. Unlike DSP or DBF, which need many high-speed DAC's, this MSP architecture can carry out adaptive beamforming functions with very low dc-power consumption. It is free from both Nyquist sampling speed and quantization error. It is potentially a significant step in the

Fig. 9. Synthesized vector accuracy of the megalithic BFN. The standard deviations of amplitude and phase errors measured for the 32 output ports are designated by (a) and (b), respectively. The circuit simulator estimates the amplitude and phase deviations resulting in the degenerated line (c). The ordinates for amplitude and phase errors have the scales that indicate equivalent effects [24] on the radiation pattern in phased array antennas.

ongoing development of multiple-carrier transmitting phased arrays in low intermodulation distortion communication channels, and of GEO/LEO satellite onboard active phased array transponders.

#### APPENDIX

To cascade circuits directly one after another without inter-stage matching networks, an “iterative impedance” technique is introduced. Iterative impedance is defined as “the input impedance of the circuit when all the output ports are terminated to the loads which have the same impedance as the input port of the circuit itself.” The iterative impedance,  $Z_{\text{itera}}$ , is formulated as

$$Z_{\text{itera}} = Z_{\text{input}}|_{Z_{\text{load}}=Z_{\text{input}}}$$

and

$$Z_{\text{itera}}^* = Z_{\text{output}}|_{Z_{\text{source}}=Z_{\text{output}}}$$

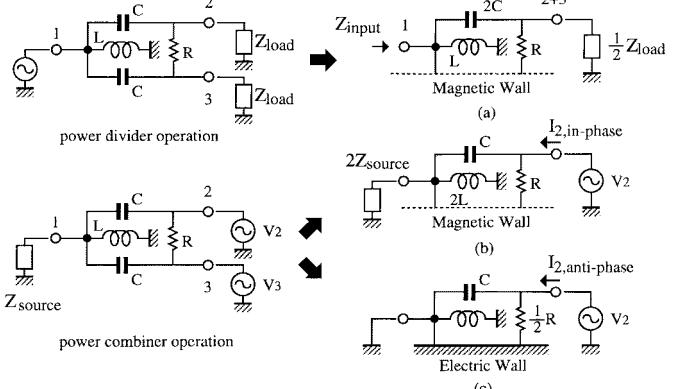

where the asterisk (\*) denotes the complex conjugate. Once the circuit finds a  $Z_{\text{itera}}$  satisfying the first formula, the second formula is accordingly satisfied at least for reciprocal networks. In this definition, it is clear that the circuit is cascadable if and only if there exists an iterative impedance for the circuit. Herein “cascadable” means being able to connect each stage after another stage. Fortunately, the circuit shown in Fig. 3 has an iterative impedance, which is analytically deduced and found to be a complex number as shown below.

Let all the two output ports be terminated to some unknown load impedance  $Z_{\text{load}}$  as shown in Fig. 10. Looking into port 1, the circuit is equivalent to the schematic shown in Fig. 10(a), thanks to circuit symmetry [23]. The input impedance  $Z_{\text{input}}$  is calculated as:

$$Z_{\text{input}} = \frac{1}{\frac{1}{2}Z_{\text{load}} + \frac{1}{2j\omega C} + \frac{1}{j\omega L}}.$$

Imposing the cascadable condition into the above, an equation for  $Z_{\text{itera}}$  is obtained as

$$j\omega C Z_{\text{itera}}^2 + (1 - \omega^2 LC) Z_{\text{itera}} - j\omega L = 0. \quad (A1)$$

Fig. 10. Analysis on complex iterative impedance for the PcpD. For power divider operation, input impedance is calculated by the even-mode equivalent circuit shown in (a). Power combiner operation is regarded as superposition of even- and odd-mode operations as shown in (b) and (c). The in- and antiphase components of current  $I_2$  are calculated by exciting  $V_2 = V_3 = 1$ , and  $V_2 = -V_3 = 1$ , respectively. Internal impedance of each voltage source is omitted for simplicity.

This equation has two complex solutions for  $Z_{\text{itera}}$ . The one that has a positive real part should be preferred for passive impedance matching.

The next step we proceed is to isolate the two output ports. Terminating port 1 with unknown  $Z_{\text{source}}$ , this circuit is regarded as the two-port network shown in Fig. 10. The current at port 2 is expressed using admittance parameters as  $I_2 = Y_{22}V_2 + Y_{32}V_3$ . With the help of topological symmetry [23] again, the circuit is equivalent to Fig. 10(b) or (c) for in- or antiphase unity voltage excitations, respectively. Therefore, the current  $I_2$  is calculated for each excitation as

$$I_{2, \text{in-phase}} = \frac{1}{\frac{1}{2Z_{\text{source}}} + \frac{1}{2j\omega L} + \frac{1}{j\omega C}}$$

and

$$I_{2, \text{antiphase}} = j\omega C + \frac{2}{R}. \quad (A2)$$

To isolate ports 2 and 3 from each other, the cross term  $Y_{32}$  should vanish or

$$I_{2, \text{in-phase}} = Y_{22} = I_{2, \text{antiphase}}. \quad (A3)$$

Another condition we should apply is the output impedance matching

$$Z_{\text{source}} = 1/Y_{22}^* \quad (A4)$$

where the asterisk (\*) denotes the complex conjugate. Substituting (A2) and (A4) into (A3), the unknown source is eliminated and the resultant formula deduces a simple relationship as

$$6L = CR^2 \text{ and } 3\omega^2 LC = 1. \quad (A5)$$

Simultaneous solutions of (A5) provide element values for the center frequency. In case that the center frequency is given first,  $L$  and  $C$  are explicitly calculated by

$$L = \frac{R}{3\sqrt{2}\omega} \text{ and } C = \frac{\sqrt{2}}{\omega R}.$$

The resistance  $R$  is not restricted here but should be optimized so that both  $L$  and  $C$  fall into practically available values. For example,  $R = 100 \Omega$  is preferred for S-band applications, resulting in  $L = 1.5 \text{ nH}$  and  $C = 0.9 \text{ pF}$  at 2.5 GHz.

The final step of the formulation deduces the iterative impedance. To solve (A1) for  $Z_{\text{itera}}$ , (A5) is used and the  $L$  and  $C$  are then eliminated. From the two possible complex solutions, we prefer the one which has the positive real part. Consequently the iterative impedance is found to be a complex number

$$Z_{\text{itera}} = Z_{\text{load}} = Z_{\text{input}} = \frac{2 + j\sqrt{2}}{6} R.$$

It goes without stating that  $Z_{\text{source}}$  or  $Z_{\text{output}}$  is conjugate to the above impedance, since this two-way divider/combiner is obviously a reciprocal circuit. The sign of the imaginary part means that the circuit has inductive input and capacitive output impedances.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. I. Toyoda, K. Ueno, K. Horikawa, M. Nakatsugawa, F. Ishitsuka, and Prof. A. S. Daryoush for participating in the valuable discussions on huge-scale MMIC design and active phased array antennas. They also wish to thank N. Sakamoto and E. Ishiyama for their excellent technical support in establishing the on-wafer multiport automatic measurement system.

#### REFERENCES

- [1] K. Ueno, T. Ohira, H. Tsunoda, and H. Ogawa, "Phased array fed single reflector antenna for communication satellites," in *Int. Symp. Antennas and Propagation*, Makuhari, Japan, Sept. 1996, vol. 2C3-3.

- [2] T. Tanaka, "Digital signal processor for digital multi beam forming antenna in mobile communication," in *IEEE Vehicular Technology Conf. Dig.*, June 1994, pp. 1507-1511.

- [3] H. Steyskal, "Digital beam forming at Rome Laboratory," *Microwave J.* (special rep.), pp. 100-126, Feb. 1996.

- [4] S. Lucyszyn and I. D. Robertson, "Analog reflection topology building blocks for adaptive microwave signal processing applications," *IEEE Trans. Microwave Theory Tech.*, vol. 43, pp. 601-611, Mar. 1995.

- [5] D. Roques, J.-L. Cazaux, and M. Pouyssegur, "GaAs MMIC control functions for 3.7-4.2 GHz band active antenna," *Ann. Telecommun.*, vol. 45, nos. 3/4, pp. 224-230, 1990.

- [6] K. A. Shalkhauser, J. A. Windyka, D. C. Dening, and M. J. Fithian, "System-level integrated circuits for phased array antenna applications," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 1996, pp. 1593-1596.

- [7] T. Ohira, I. Toyoda, and H. Ogawa, "Single chip variable beam forming network for 64-element array radiators," in *Proc. 26th Eur. Microwave Conf.*, Prague, Czech Republic, Sept. 1996, pp. 956-959.

- [8] F. Coromina, J. Traveset, J. L. Corral, Y. Bonnaire, and A. Dravet, "New multibeam beam forming networks for phased array antennas using advanced MMCM technology," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 1996, pp. 79-82.

- [9] G. Estep, R. Gupta, T. Hampsch, M. Zaharovits, L. Pryor, C. Chen, A. Zaghoul, and F. Assal, "A C-band beam-forming matrix for phased-array antenna applications," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 1995, pp. 1225-1228.

- [10] J. Butler and R. Lowe, "Beam-forming matrix simplifies design of electronically scanned antennas," *Electron. Design*, vol. 9, pp. 170-173, Apr. 1961.

- [11] F. Ishitsuka, N. Iwasaki, Y. Ando, N. Kukutsu, and T. Ohira, "High-frequency performance of a novel RF interconnection system with miniaturized in-line coaxial connectors," in *IEEE CPMT 3rd VLSI Packaging Workshop Jpn.*, Kyoto, Japan, Dec. 1996, pp. 142-143.

- [12] R. C. Waterman, Jr., W. Fabian, R. A. Pucel, Y. Tajima, and J. L. Vorhaus, "GaAs monolithic Lange and Wilkinson couplers," *IEEE Trans. Electron Device*, vol. ED-28, pp. 212-216, Feb. 1981.

- [13] G. E. Brehm and R. E. Lehmann, "Monolithic GaAs Lange coupler at X-band," *IEEE Trans. Electron Devices*, vol. ED-28, pp. 217-218, Feb. 1981.

- [14] R. K. Gupta and W. J. Getsinger, "Quasilumped-element 3- and 4-port networks for MIC and MMIC applications," in *IEEE MTT-S 1984 Int. Microwave Symp. Dig.*, pp. 409-411.

- [15] J. Staudinger, "An ultra wide bandwidth power divider on MMIC operating 4 to 10 GHz," in *IEEE 1989 Microwave and Millimeter-Wave Monolithic Circuit Symp.*, pp. 127-131.

- [16] T. Hirota, A. Minakawa, and M. Muraguchi, "Reduced-size branch-line and rat-race hybrids for uniplanar MMIC's," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 270-275, Mar. 1990.

- [17] J. Staudinger and W. Seely, "An octave bandwidth 90° coupler topology suitable for MMIC's," *Microwave J.*, vol. 33, pp. 117-130, Nov. 1990.

- [18] S. Banba and H. Ogawa, "Multilayer MMIC branch-line hybrid using thin dielectric layers," *IEEE Microwave Guided Wave Lett.*, vol. 1, pp. 346-347, Nov. 1991.

- [19] M. C. Tsai, "A new compact wide band balun," in *1993 IEEE MTT-S Int. Microwave Symp.*, pp. 141-143.

- [20] S. Banba and H. Ogawa, "Multilayer MMIC directional couplers using thin dielectric layers," *IEEE Trans. Microwave Theory Tech.*, vol. 43, pp. 1270-1275, June 1995.

- [21] T. Gokdemir, I. D. Robertson, Q. H. Wang, and A. A. Rezazadeh, "K/K-band coplanar waveguide directional couplers using a three-metal-level MMIC process," *IEEE Microwave Guided Wave Lett.*, vol. 1, pp. 76-78, Feb. 1996.

- [22] K. Nishikawa, T. Tokumitsu, and I. Toyoda, "A novel miniature Wilkinson divider using aperture-ground plane and application to 3D-MMIC K-band receiver," *IEEE Microwave Guided Wave Lett.*, vol. 6, pp. 372-374, Oct. 1996.

- [23] J. Reed and G.J. Wheeler, "A method of analysis of symmetrical four-port networks," *IRE Trans. Microwave Theory Tech.*, vol. MTT-4, pp. 246-252, Oct. 1955.

- [24] R. J. Mailloux, *Phased Array Antenna Handbook*. Norwood, MA: Artech House, 1994, pp. 395-399.

**Takashi Ohira** (S'79-M'83) was born in Osaka, Japan, in 1955. He received the B.E. and D.E. degrees in communication engineering from Osaka University, Osaka, Japan, in 1978 and 1983, respectively.

In 1983, he joined NTT Electrical Communication Laboratories, Yokosuka, Japan, where he was engaged in research on monolithic integration of microwave semiconductor devices and circuits. From 1987 to 1992, he was a Senior Research Engineer at NTT Radio Communication Systems Laboratories, Yokosuka, Japan, where he was responsible for the development of GaAs MMIC transponder modules for Japanese domestic multibeam communication satellites. He is currently a Senior Research Manager of NTT Wireless Systems Laboratories, Yokosuka, Japan. He is a member of ETS-VIII satellite development committee. He is working on the design of multifunction and large-scale MMIC's for future microwave signal processor applications.

Dr. Ohira was awarded the 1986 Shinohara Prize by the Institute of Electronics and Communication Engineers of Japan. He serves as IEEE MTT-S Tokyo chapter secretary, IEEJ millimeter- and submillimeter-wave device research committee officer, and APMC'98 steering committee vice general officer.

**Yoshinori Suzuki** received the B.E. and M.E. degrees from Tohoku University, Sendai, Japan, in 1993 and 1995, respectively.

He joined NTT Wireless Systems Laboratories, Yokosuka, in 1995. He has been engaged in research on monolithic microwave integrated circuits for satellite onboard phased array beamforming networks.

Mr. Suzuki is a member of the Institute of Electronics, Information, and Communication Engineers (IEICE) of Japan.

**Hiroyo Ogawa** (M'84) received the B.S., M.S., and Dr. Eng. degrees in electrical engineering from Hokkaido University, Sapporo, in 1974, 1976, and 1983, respectively.

He joined the Yokosuka Electrical Communication Laboratories, Nippon Telegraph and Telephone Public Corporation, Yokosuka, in 1976. He has been engaged in research on microwave and millimeter-wave integrated circuits, monolithic integrated circuits, and development of subscriber radio systems. From 1985 to 1986, he was a Post-Doctoral Research Associate at the University of Texas at Austin, on leave from NTT. From 1987 to 1988, he was engaged in design of the subscriber radio equipment at the Network System Development Center of NTT. From 1990 to 1992, he was engaged in the research of optical/microwave monolithic integrated circuits and fiber optic links for personal communication systems at ATR Optical and Radio Communication Research Laboratories. Since 1993, he has been researching on microwave photonics, and microwave and millimeter-wave signal processing techniques for communication satellites at NTT Wireless Systems Laboratories.

Dr. Ogawa is a member of the Institute of Electronics, Information, and Communication Engineers (IEICE) of Japan.

**Hideki Kamitsuna** (M'91) was born in Hiroshima, Japan, in 1963. He received the B.S. and M.S. degrees in physics from Kyushu University, Fukuoka, Japan, in 1986 and 1988, respectively.

In 1988, he joined NTT Radio Communication Systems Laboratories, Yokosuka, Japan, where he was engaged in research on MMIC's. In 1990, he joined ATR Optical and Radio Communications Research Laboratories, Kyoto, Japan, where he was engaged in research on MMIC's, optical/microwave monolithic integrated circuits and fiber optic links for future personal communication systems. In 1993 to 1995, he was with NTT Wireless Systems Laboratories, Yokosuka, Japan, where he was engaged in monolithically integrated photoreceivers for optical/microwave interaction systems. Since 1996, he has been with NTT Electronics Corporation, Yokosuka, Japan. He is currently working on MMIC's for satellite onboard phased array systems.

Mr. Kamitsuna received the Young Engineer Award from the Institute of Electronics, Information and Communication Engineers (IEICE) of Japan in 1995.